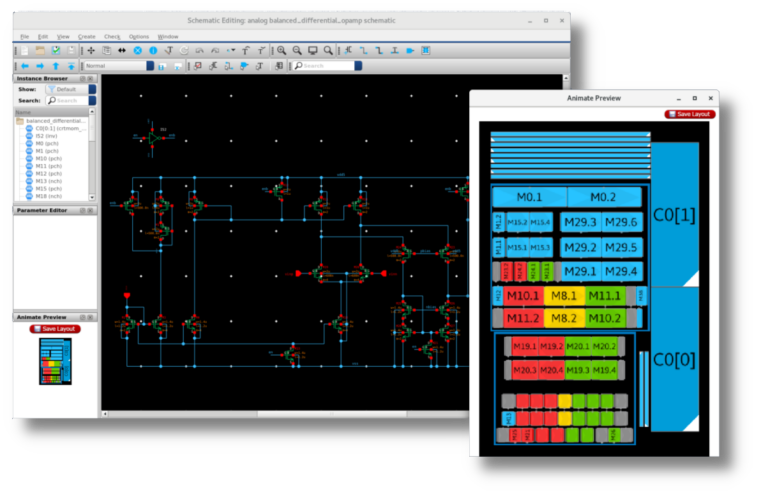

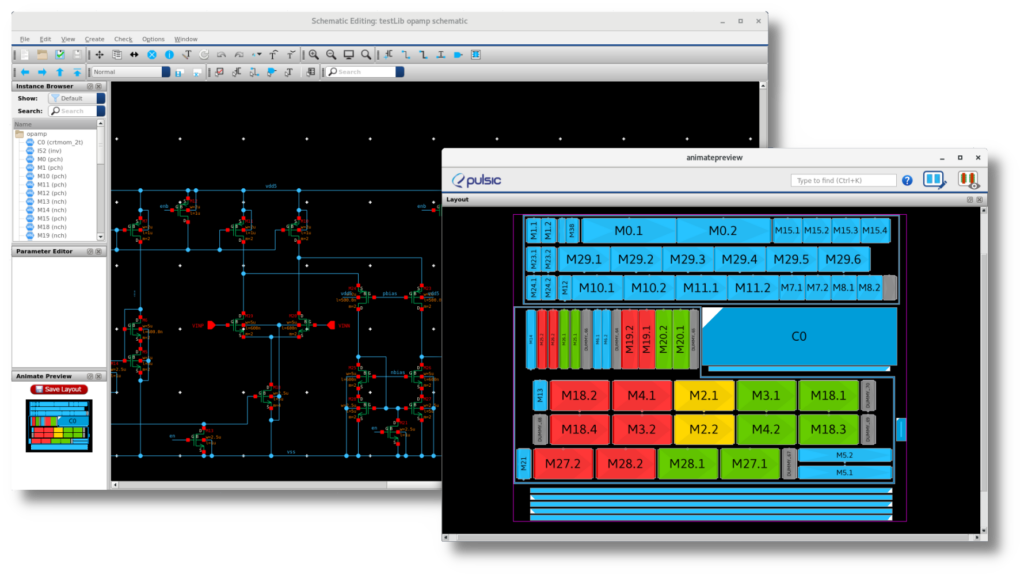

Animate Preview

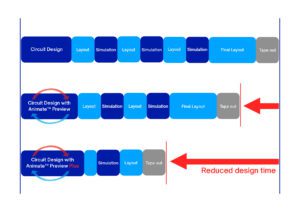

Initial layout created in seconds by Animate Preview helps you to make better design decisions in less time

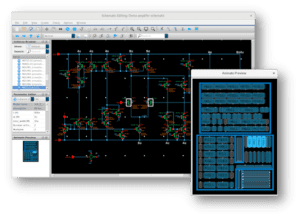

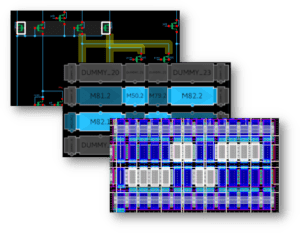

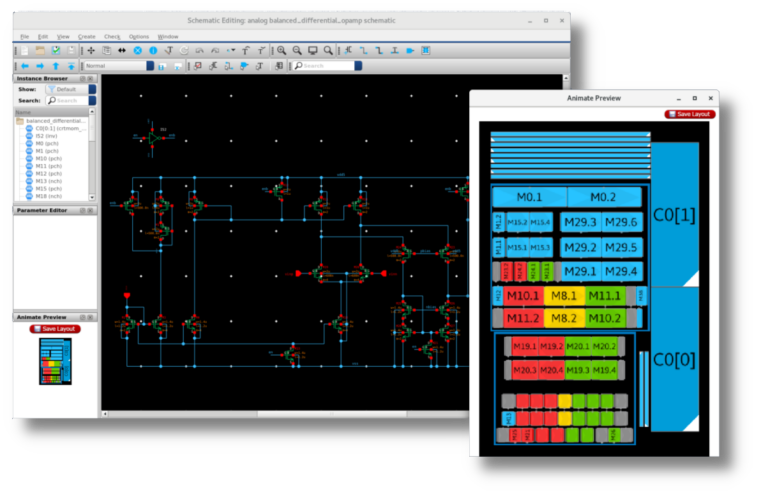

Animate Preview gives you quick, easy, and accurate physical information about your analog circuit while you develop your schematic. Giving you a detailed initial layout of your circuit and helping you to spot problems.

Pulsic’s Animate Preview helps you to visualize the layout so that you can make better decisions earlier in your design flow, reduce costly iterations and optimize your design process.

Watch the demo

Paul Clewes (VP of Research and Development at Pulsic) demonstrates Animate Preview.

Download Animate Preview

Accelerate your analog design flow – download Animate Preview today

System Requirements

Cadence® Virtuoso® IC6.1.8, IC23.1 or ICADV 20.1

Enter your details below to download Animate Preview now